- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT821054PQF (IDT, Integrated Device Technology Inc)IC PCM CODEC QUAD MPI 64-PQFP

26

IDT821054 QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

INDUSTRIAL TEMPERATURE RANGE

CS[1:0] = 10:

transmits data on falling edges of BCLK, receives data on falling edges of BCLK.

CS[1:0] = 11:

transmits data on falling edges of BCLK, receives data on rising edges of BCLK.

The PCM data Offset Configuration bits (OC[2:0]) determine that the transmit and receive time slots of PCM data offset from the FS

signal by how many periods of BCLK:

OC[2:0] = 000:

0 period of BCLK (default);

OC[2:0] = 001:

1 period of BCLK;

OC[2:0] = 010:

2 periods of BCLK;

OC[2:0] = 011:

3 periods of BCLK;

OC[2:0] = 100:

4 periods of BCLK;

OC[2:0] = 101:

5 periods of BCLK;

OC[2:0] = 110:

6 periods of BCLK;

OC[2:0] = 111:

7 periods of BCLK.

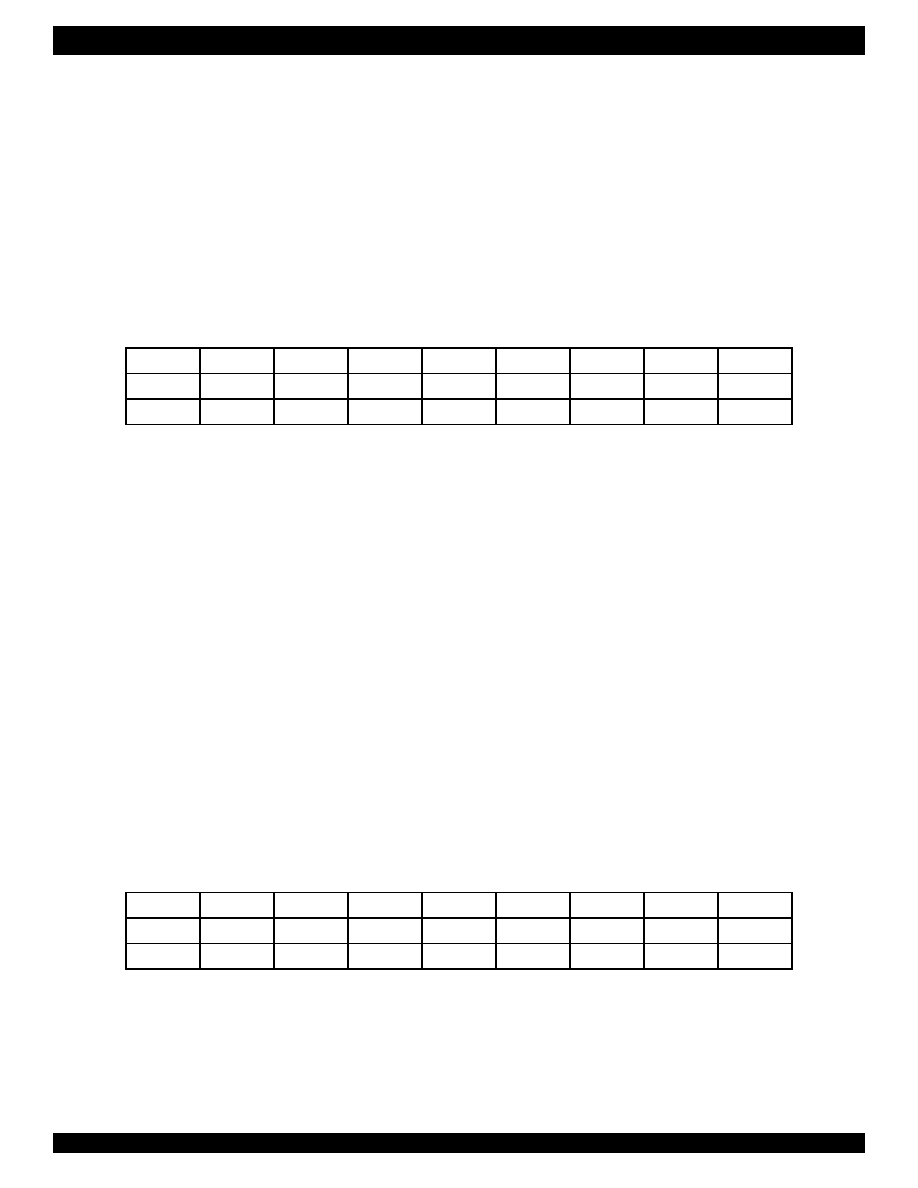

GREG8: SLIC Ring Trip Setting and Control, Read/Write (27H/A7H)

The Output Polarity Indicator bit (OPI) indicates the valid polarity of output:

OPI = 0:

the selected output pin changes from low to high to activate the ring (default);

OPI = 1:

the selected output pin changes from high to low to activate the ring.

The Input Polarity Indicator bit (IPI) indicates the valid polarity of input:

IPI = 0:

active low (default);

IPI = 1:

active high.

The Input Selection bit (IS) determines which input will be selected as the off-hook indication signal source.

IS = 0:

SI1 is selected (default);

IS = 1:

SI2 is selected.

The Ring Trip Enable bit (RTE) enables or disables the ring trip function block:

RTE = 0:

the ring trip function block is disabled (default);

RTE = 1:

the ring trip function block is enabled.

The Output Selection bits (OS[2:0]) determine which output will be selected as the ring control signal source.

OS[2:0] = 000 - 010:

not defined;

OS[2:0] = 011:

SB1 is selected (when SB1 is configured as an output);

OS[2:0] = 100:

SB2 is selected (when SB2 is configured as an output);

OS[2:0] = 101:

SB3 is selected (when SB3 is configured as an output);

OS[2:0] = 110:

SO1 is selected;

OS[2:0] = 111:

SO2 is selected.

GREG9: SI Data, Read Only (28H)

The SIA[3:0] bits contain the debounced data (off-hook status) on the SI1 pins of Channel 4 to Channel 1 respectively.

The SIB[3:0] bits contain the debounced data (ground key status) on the SI2 pins of Channel 4 to Channel 1 respectively.

b7

b6

b5

b4

b3

b2

b1

b0

Command

R/W

0

1001

11

I/O data

OPI

Reserved

IPI

IS

RTE

OS[2]

OS[1]

OS[0]

b7

b6

b5

b4

b3

b2

b1

b0

Command

00

1010

00

I/O data

SIB[3]

SIB[2]

SIB[1]

SIB[0]

SIA[3]

SIA[2]

SIA[1]

SIA[0]

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3001APVG8

IC PLL WAN W/SGL REF INP 56-SSOP

IDT82V3010PVG

IC PLL WAN 51/E1/OC3 DUAL 56SSOP

IDT82V3011PVG

IC PLL WAN T1/E1/OC3 SGL 56-SSOP

IDT82V3012PVG8

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

IDT82V3155PVG

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

IDT82V3202NLG

IC PLL WAN EBU SGL 68-VFQFPN

IDT82V3255TFG

IC PLL WAN SMC STRATUM 3 64-TQFP

IDT82V3280APFG

IC PLL WAN SE STRATUM 2 100TQFP

相关代理商/技术参数

IDT821054PQFG

功能描述:IC PCM CODEC QUAD MPI 64-PQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821064

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE

IDT821064PQF

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE

IDT821068

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC

IDT821068PX

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC

IDT821621

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LONG HAUL SLIC

IDT821621J

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LONG HAUL SLIC

IDT8217LP35P

制造商:Integrated Device Technology Inc 功能描述: